八英寸晶圆厂的“问题”

保守来讲,当下8英寸(200mm)晶圆的供应链情况相当严峻!

然而,这绝不是新问题。中国台湾的市场调查公司一一TrendForce于2020年11月发布新闻称:“就8英寸晶圆的产能而言,自2019年下半年以来一直持续在严重的供给不足问题”。

此外,雪上加霜的是2021年3月瑞萨电子那珂工厂发生了火灾。由于瑞萨的此处工厂为诸多车型供货,因此导致问题更加恶化。

基于以上背景,导致诸多因素“纠缠”在一起。但是,不言而喻,最大的原因还是在于新冠疫情(COVID-19)。由于新冠疫情的发生,耳机、电脑、电视、显示屏、手机等各种电子产品的需求猛增。

虽然汽车也属于以上范畴,但人们还是希望汽车市场会在2021年内从新冠疫情的阴影中恢复。如今各种产品都在推广将多种功能汇集于一体的SoC(System on Chip)模式,因此很多产品都需要搭载多个具备数模混合信号(Mixed Signal Chip)的IC。以上产品的用途方向主要有以下:PMIC(Power Management IC)、CMOS图像传感器、指纹识别传感器、汽车发动机/底盘控制、显示屏驱动IC、Sub Giga Hertz的无线通信芯片等。一般情况下,以上这些都适用180纳米、350纳米工艺,用8英寸晶圆生产。

即,用于这种数模混合信号芯片(Mixed Signal Chip)、功率半导体的产品需求不断增长,这导致了8英寸晶圆的产能不足。

受到8英寸晶圆的供给达到极限的影响,代工厂(Foundry)很有可能会扩大产能。代工厂可能会收购垂直统筹型厂家(IDM:Integrated Device Manufacturer)的8英寸晶圆生产设备和产线。可列举的事例如下:最近有报道指出,中国台湾的UMC正在讨论收购Japan Semiconductor(原东芝的半导体制造公司) 的8英寸产线。

没有供生产厂家

正如Trend Force的报道指出的一样,自2019年下半年开始的严重的半导体供给不足问题,可以推测的原因是几乎没有厂家可以生产出8英寸晶圆的设备,即使现在也是如此,因此半导体生产设备的价格不断高涨。

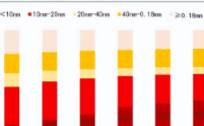

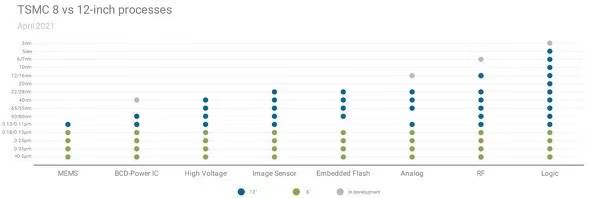

TSMC的采用8英寸、12英寸晶圆的工艺。(图片出自:eetimes)

此外,8英寸晶圆的价格较12英寸低得多,因此,代工厂普遍认为扩大8英寸产能的成本效率更差。因此,产生了一系列连锁反应,如一部分代工厂就对客户提高了8英寸晶圆的价格。

换句话说,就8英寸晶圆的情况而言,与其说“供应链混乱”,不如说其特点是“供应厂家不足”。

一部分“移步”12英寸晶圆

就12英寸(300mm)晶圆的代工厂而言,以TSMC、GLOBALFOUNDRIES为代表的各家企业为扩大产能而在火热地投资,然而,却看不到任何有关8英寸的改善情况。

由于8英寸晶圆产能没有任何改善,因此一部分厂家正在从现有的180nm、350nm的8英寸产线转为使用12英寸晶圆。此外,很多代工厂可以提供用12英寸晶圆生产的130nm工艺,因此可用作二次供给源或者主要供给源。因此,这有助于提高供应链的地理多样性。

80纳米、130纳米工艺技术的特征

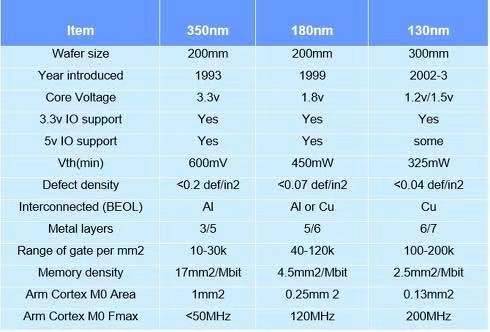

180纳米和130纳米工艺虽然有类似的工艺,但也有不同的地方。主要是晶体管的阈值电压的下降程度不同,核心供给电压为1.8V一1.5V,或者低至1.2V。此外,由于存在各种工艺技术的选择项,因此可以支持5V/3.3V的IO电压,就对于模拟/RF设计极其重要的被动零部件而言,这些工艺特征极其类似。

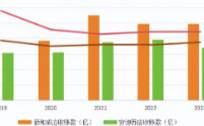

用于Mixed Signal ASIC等产品的主要节点技术比较图。(图片出自:eetimes)

12英寸晶圆技术有多个优势。由于可代替旧代际技术中的铝而使用铜,因此电流密度允许值也较高,耐电迁移性也较优秀。此外,金属层的层数也较多,晶体管尺寸较小,因此,通过提高晶体管密度、布线密度,可以缩小芯片尺寸、提高性能。

此外,大部分180纳米工艺技术和大部分的130nm BCD(Bipolar-CMOS-DMOS)工艺技术都可以支持STI(Shallow Trench Isolation,浅槽隔离)等功能,因此与大部分在350纳米技术中使用的LOCOS(Local Oxidation of Silicon)绝缘相比,因此可以获得较高的密度、闩锁效应(Latch Up)保护机能等。因此,达到提高线路性能和稳定性的效果。

如今,130纳米 BCD工艺已经相当成熟,因此可作为各种工艺技术的选择项。如不同级别的高压晶体管、非挥发性存储半导体、MIM(金属一一绝缘膜一一金属)电容、稳压二极管(Zener)/肖特基二极管等。因此,不仅可以将复杂的模拟/RF功能与SoC解决方案融合,还可以提供其他优势。

8英寸晶圆还有很多优势

8英寸晶圆还有很多优势,比方说,用350纳米制造的8英寸晶圆的价格优势。

原因如下:生产设备已经完成折旧、生产工艺相对简单(层数少)。此外,一部分模拟线路未必能够在新工艺中顺利实现微缩化,因此与130纳米同等程度的半导体芯片的价格可能会高于350纳米。但是,当因零部件不足导致无法生产产品时,大部分情况下会发生极其严重的情况,而不是单纯的半导体芯片的成本差。

此外,现阶段人们的关注点是尽管各家代工厂都在从8英寸转到12英寸,但却没有一家厂家做出任何发言。对于Mixed Signal ASIC熟练的厂家虽然在努力,但首先应该着手于线路图的端口、IC 的数据手册(Data Sheet)。

就为重新设计ASIC所需的投资而言,应该统筹一下其他产品,以免同样受到如8英寸供应链同样问题。

130纳米的特征尺寸(Feature Size)较小,因此可以在不增加成本的情况下与“Arm Cortex-M”系列核融合。低端CPU所需要的芯片面积仅为数平方毫米,而且有可能以较高的效率与64kbit/128kbit的SRAM融合。

从如今的数据手册来看,从设计ASIC、量产、获得认证的日程需要14个月一一24个月(依复杂程度而定),最初的Proto Type Silicon应该可以在一年内完成。如果是车载产品,从制作规格书到PPAP(Production part approval process,生产件批准程序)大概需要24个月一一36个月(依复杂程度而定)。130纳米ASIC的一般预算为60万美元起步(依据实际的复杂程度和IP知识产权内容而定),如果依据AEC-Q100的话,费用为400万美元左右。如今,130纳米工艺(12英寸晶圆)的Mask Tool的成本为20万美元以下,占整体成本的比例较低。

很多Mixed Signal Device都是由供给不足的8英寸晶圆制造的,由于8英寸晶圆产线的投资不足(原因是投资收益率低下),未来供应链问题还会继续存在。

此次的半导体供给不足问题某种程度上是一个“警告”,如今使用8英寸晶圆的企业应该首先考虑一下未来的需求。此外,无论是主要生产据点,还是第二供应商(Second Source),在所有的工艺完成之前都需要确保足够的时间。

本文转载至微信公众号“ 半导体行业观察 ”, 贝壳投研经授发布。

飞鲸投研从多维度分析,整理了一份《成长50》的名单,可以关注同名公众号:"飞鲸投研":feijingtouyan,进行领取(点击复制)

/阅读下一篇/