浅谈台积电的先进封装

本文转载至微信公众号“半导体行业观察”,作者 畅秋,贝壳投研经授发布。

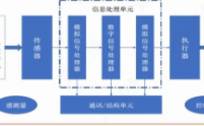

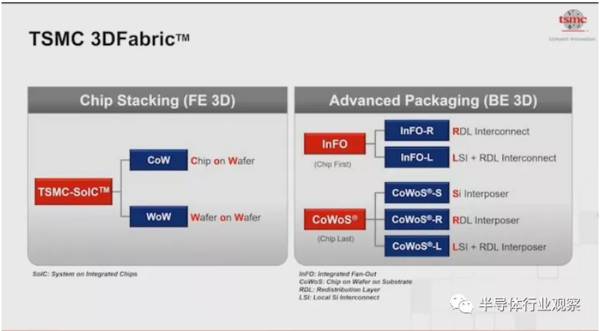

Die-to-die ,ODI ,TSV所有这些单词和首字母缩略词都有着相同点——它们都与两块硅的物理连接有关。一般来说有多种方法将多个芯片连接在一起,而台积电有许多这样的技术。为了统一技术,它将其命名为2.5D和3D封装等。最近台积电推出了有一种新的封装解决方案DFabric。3DFabric将台积电提供的十几种包装技术结合起来,总的来说,3DFabric分为两个部分:一边是所说的“前道”芯片堆叠技术,如Cow(Chip on wafer);另一边是“后道”封装技术,如InFO (Integrated Fan-Out)和CoWoS (chip-on-wafer -on- substrate)。

台积电引入了许多的专业的术语,如RDL或LSI等,这些术语有别于英特尔的术语,下文中我们会做详细的解释:

前道芯片堆叠技术,被统称为“SoIC”,或集成芯片系统。这些技术的主要的特征峰是不会使用后端集成用到的凸点技术,而是直接将硅片堆叠到一起。就好似是一整个硅片一样。

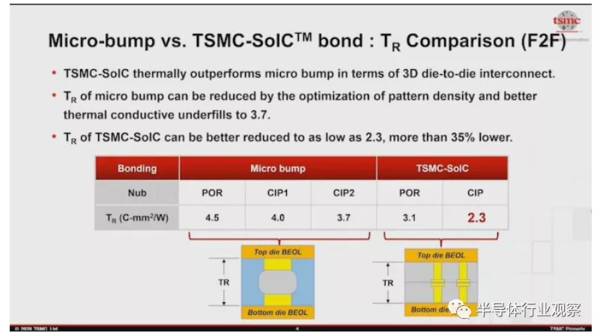

这种技术相对来说更加的复杂,但是在热阻方面有着很大的有优势。

如下图所示 SoIC连接的热电阻比微凸连接低35%,随着封装技术的发展芯片的 集成度越高,这种连接出的热阻是一个非常大的挑战。然而这些SoIC技术的缺点是堆叠设计必须与其他芯片共同设计并且在最开始芯片设计方案就需要确定下来,然而微凸点技术只是需要后期把芯片连接在一起。

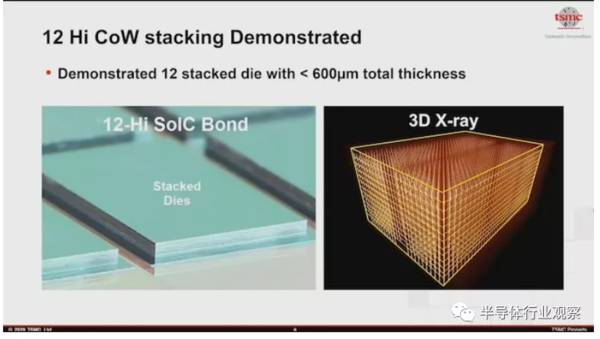

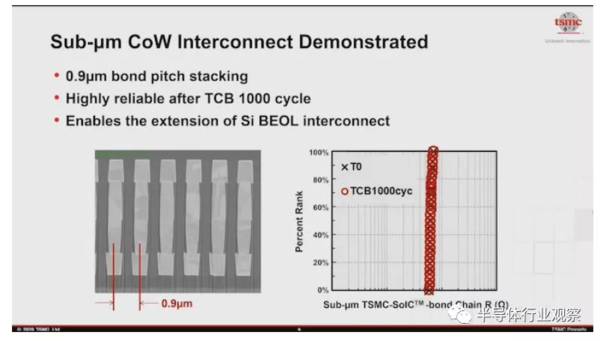

虽然有上述的缺点但是台积电仍然努力的推销它的SoIC技术。在一般情况下人们自然会担心这种连接的可靠性,和连接密度。但是台积电表示,它们可以实现0.9微米的键合间距。相比于因特尔它们的间距提高了两个数量级。

台积电计划在其7纳米,五纳米和三纳米工艺节点上为客户提供SoIC技术,届时TSV 的间距将从9微米缩减到4.5微米。

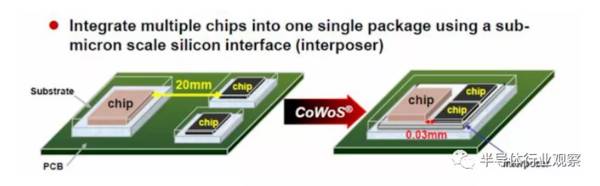

台积电后道先进封装有三种形式,大多数人都熟悉的一种方法是转接板方法,在所有互连的芯片下面放置一大块硅,这是一种比简单地通过PCB封装更好的布线方法。

另一种方法是,与之类似,转接板是嵌入在PCB中,只用于连接一个特定的芯片到另一个(英特尔叫这种方法为的嵌入式多芯片互连桥,或EMIB)。

第三种是直接垂直堆叠,然而这与上面提到的SoIC实现方式不同,因为在两片硅之间使用微凸点,而SoIC并不使用。事实上,台积电有一半的产品中所有的实现都是基于微凸点的——不同芯片之间可以更好地混合和匹配场景,但它没有获得SoIC提供的密度或功率优势。这就是为什么它被称为“后道”高级封装——例如,支持hbm的GPU。

许多支持HBM的GPU有一个GPU芯片,几个HBM芯片,都放置在一个转接板上。GPU和HBM是由不同的公司制造的(甚至可以使用不同的HBM),而转接板也可以在其他地方制造。这个转接板可以是无源的(不包含逻辑,只有模对模路由),也可以是有源的,如果需要的话,可以为许多的芯片实现连接,尽管这意味着消耗电力。台积电的将这种封装的形式叫做CoWoS,根据技术的不同的类型,CoWoS有三个方案。

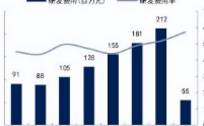

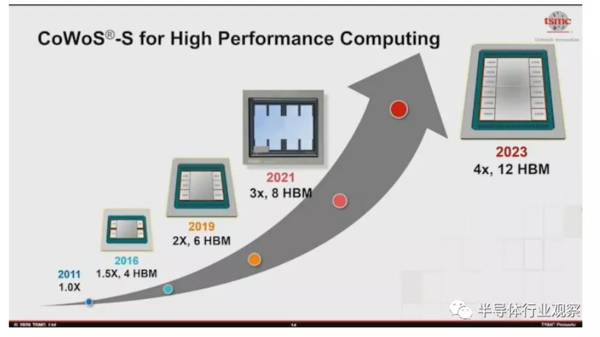

大家都熟悉的是CoWoS, S代表Silicon Interposer。通常是在65 nm 的制程中制造,因为是一整块的单晶片,所以必须以同样的方式制造,随着我们进入小芯片的时代,需要有更多的芯片集成所以转接板的尺寸越来越大,但是受到掩模版尺寸的限制,所以台积电研发出了大于掩模版尺寸的技术,根据他的路线图道2023年,这些转接板的尺寸将四倍于掩模版。

台积电也正在实现一个名为CoWoS – S STAR的技术方案,用于标准架构。这将允许客户在2/4/6 HBM堆栈的特定设计协议下工作,最小化转接板的尺寸,同时也加快了上市时间并提高产量。

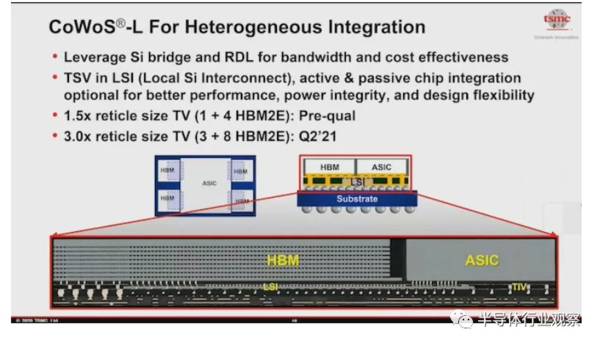

CoWoS - l是另一种方案,使用本地硅互连和再分布线层。这里的关键词是“本地”,意思是它在将两个硅晶片连接在一起。这将是台积电应对英特尔EMIB的方式。虽然英特尔的EMIB已经用于多个产品(Kaby-G, Stratix 10, Agilex FPGA),但台积电目前仅处于验证阶段。

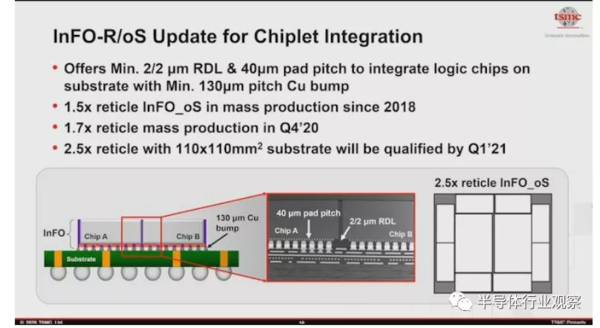

InFO(集成扇出)封装允许芯片在SoC的标准平面之外“扇出”额外的连接增加I/O接口。台积电多年来一直提供InFO,但在3DFabric下,它现在将提供与包内连接相关的不同类型的InFO。InFO-R(也称为InFO_oS)允许在芯片和微凸点之间添加再分配层,以便将多个芯片给封装到一起。这种技术的限制因素也是掩模版的尺寸。

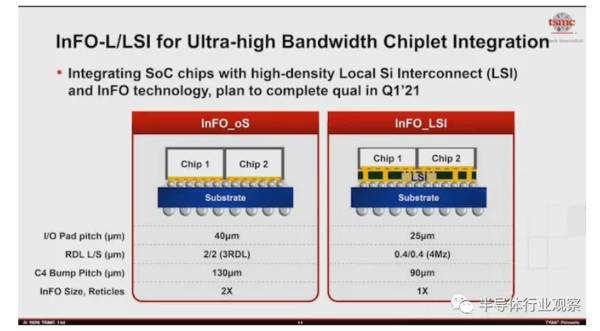

InFO- l与CoWoS - l类似,它使用一个局部的硅互连将多个InFO芯片连接在一起。这项技术仍在进行中。

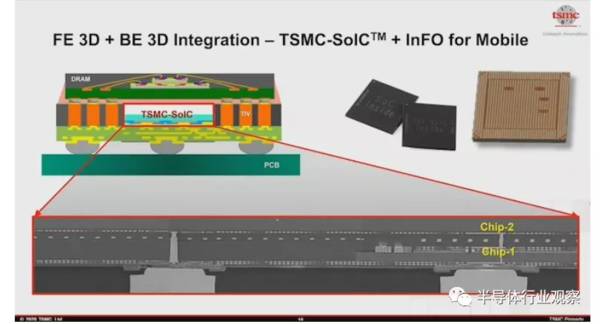

TMSC的封装技术也可以组合在同一产品中。通过实现前端(SoIC)和后端(InFO)封装,可以制造新的产品类别。该公司制作了一个这样的模型:

台积电,只是说“3 D fabric”可能意味着很多东西,但是CoWoS-S CoWoS-L之间的区别也很难用几句话来解释清楚的。

飞鲸投研从多维度分析,整理了一份《成长50》的名单,可以关注同名公众号:"飞鲸投研":feijingtouyan,进行领取(点击复制)

/阅读下一篇/